- Sectors

- Aerospace & Defense

- Big science

- Biotechnology

- Fintech

- Insights

IMAGE COPYRIGHT: Airbus & ESA

EUTELSAT’s QUANTUM satellite is a revolutionary step forward for commercial communications satellites, offering very high customization and flexibility. It will supply services with unprecedented in-orbit reconfigurability in coverage, frequency and power, allowing complete mission rehaul, including orbital position. The satellite developed by Airbus together with ESA includes a new groundbreaking multibeam active antenna payload which is a first for commercial satellite communications in Europe.

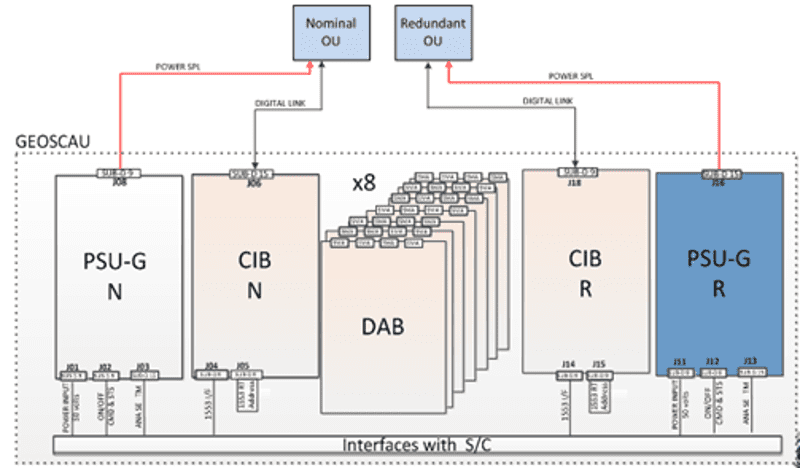

The Geolocation Signal Conditioner Unit (GEO-SCAU) relies on two complex FPGAs to run the functionality of the Capture & Interface Board (CIB) and the Digital Acquisition Board (DAB).

ARQUIMEA was tasked to carry out the design and coding of two Microsemi RTAX-S radiation tolerant FPGAs and further verification according to the ECSS-Q-ST-60-02C space standard.

COPYRIGHT: ANDRA (Agence Nationale pour la gestion des déchet radioactifs)

The FPGAs functionality can be summarized as follows:

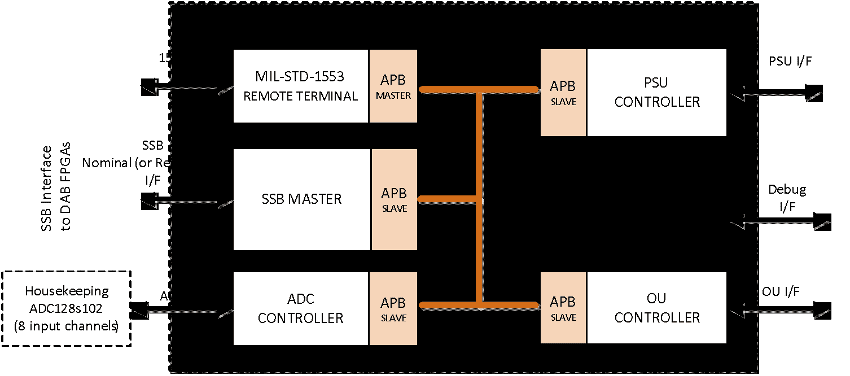

CIB FPGA

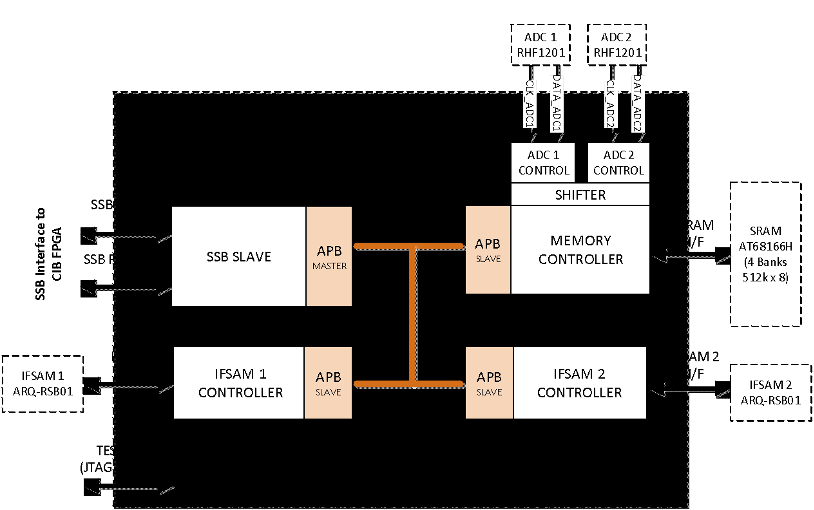

DAB FPGA

Development of complex digital FPGA design considering different interfaces in conjunction with different communication protocols, and management of telecommands & telemetries.

ARQUIMEA implemented the required logic into the two flight FPGAs, following a development flow based on the ECSS-Q-ST-60-02C space standard, including design, programming and verification.

The design was successfully completed for the two FPGA devices. A prototype was implemented and validated by programming a ProASIC3 device, while the flight models were produced and validated in the space-qualified RTAX-S devices from Microchip. The FPGA programming and hardware validation was done by ARQUIMEA at Airbus facilities.

The FPGAs were assembled in the GEO-SCAU system and the EUTELSAT QUANTUM satellite completed the qualification phase. The launch of the spacecraft is scheduled for 2020.