- Sectors

- Aerospace & Defense

- Big science

- Biotechnology

- Fintech

- Insights

Flash-based FPGAs are relatively new products in the portfolio of space-grade FPGAs and the development flow for space-related requirements is not fully proven yet through extensive learning and customer feedback dynamics.

Although not initially developed for space harsh-environment, Microsemi’s 3rd product generation of flash-based FPGAs, known as IGLOO2 and PROASIC3, are widely used in space applications thanks to the radiation tolerance of the flash-based configuration and the implementation of specific design technics against radiation effects. The 4th generation (RT Polarfire and RTG4) intended for conventional space applications such as high-performance on-board computing and high-bandwidth data processing payload, already implements rad-hard high-performance programmable resources, digital, memories, PLL, and I/O interfaces. Automatic execution of SEU mitigation techniques and SET filtering is allowed through Synthesis and Place & Route tools, respectively.

Since these devices are relatively new, their space heritage and radiation data are quite limited compared to other more mature solutions like Microsemi’s RTAX anti-fuse family. The proper implementation of SEU and SET mitigation techniques is difficult to confirm and verify in an automatic and thorough manner, since formal verification EDA tools, such as Synopsys Formality and Mentor Formal Pro, cannot confirm logic equivalence of a rad-hard design against its unmitigated counterpart, and verify its proper implementation in the specified areas. This could lead to potential design weaknesses and unexpected failures under radiation. On the other hand, former studies led by Airbus Defense & Space in collaboration with NASA/GSFC have shown SEE radiation sensitivity on RTG4 FPGA fabric and configuration cell re-programmability.

To better understand Microsemi’s 3rd and 4th generation of flash-based FPGAs and their performance against radiation, ESA issued a contract to ARQUIMEA with the following objectives:

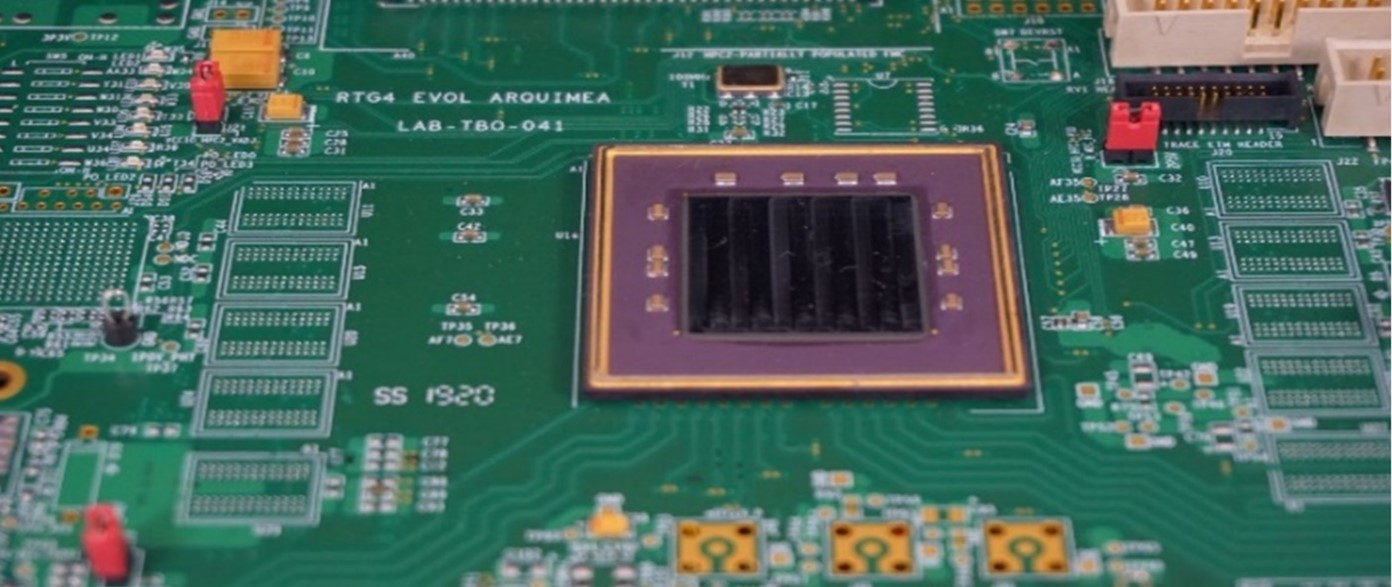

The activity required the development of several complex test vehicles on the RTG4 FPGA to validate the impact under heavy-ion and proton radiation of the FPGA fabric and SEU/SET mitigated designs compared to their unmitigated counterparts. In addition, the planning constraints and the potential damage of RTG4 FPGAs due to back-grinding operations or electrical failure were considered as the main risks of the project.

ARQUIMEA led a consortium that carried out the design of rad-hard integrated circuits running on the RTG4, as well as verification tools to prove the equivalence of the designs with and without SEE mitigation techniques. The devices were validated under radiation using ARQUIMEA’s own proprietary SEE test setup.

Validating a technology against radiation requires a careful analysis of the available data from former characterization activities, as it is the case for RTG4 FPGA, to first draw a strategic plan for the obtention of the worthiest complementary results and allow then highlighting possible hidden weaknesses under radiation environment. The approach is based on Dynamic Evaluation Circuits (DEC) that include structures such as Windows Shift registers, Ring Oscillators, Input and Output interfaces, POR, SERDES, PLL, etc. with slight variations between them (SET filtering, logic size, clock tree design, int/ext PLL etc.), to characterize the so-called fabric resources and allow covering the technology features. The Representative Evaluation Circuits (RIC) include IP cores like ARM M0, SpW Codec, CCSDS121 or CAN bus and complement the DEC results by allowing a better understanding of the impact of complementary custom SEU mitigation technics. Various frequencies, biasing or operating mode were proposed under radiation to evaluate the influence of the test conditions.

SEE TEST SETUP

ARQUIMEA’s radiation setup is controlled and monitored by a computer running the company’s own proprietary RTCAS software. The computer is connected to the hardware through an Ethernet connection, commonly available in radiation facilities. The hardware setup is modular and has a motherboard implementing Smart Fusion 2 FPGAs and a set of daughter boards.

A system self-check is implemented to analyze its correct behavior before the radiation test starts. The motherboard holds the main connectors to the rest of the PCBs and contains the logic used for temperature control, supply configuration and latch-up detection. The daughter board allows control and monitoring over 800 pins with a frequency above 400MHz. At least two of the daughter boards oversee the counting of the SEU and SEFI configuration and detection.

The RTG4 FPGAs were mounted in separate DUT boards and could be easily plugged to the system. Depending on the chip size and pinout, several DUTs could be mounted in one daughter board. It allows saving beam time by avoiding board handling during radiation testing. For proton testing, the DUT boards were separated from the daughter board through adequate cabling and shielding to avoid electronic degradation.

Two SEE campaigns were conducted on the RTG4 FPGA under heavy ion and proton in November 2019. The measurements confirmed the results from Microsemi and NASA/GSFC. Nonetheless, the following behavior were observed:

Disclaimer: The view expressed herein can in no way be taken to reflect official opinion of the ESA.